在特定个别频率上对运营商进行禁止避免与本地射频服务相冲突

发布时间:2024/5/7 23:15:49 访问次数:68

这种TDD(时分双工)信号是与现有的FDD(频分双工)DSL信号的主要区别。

G.fast的带宽将扩展到106兆赫(有可能高达212兆赫),起始频率在2.2兆赫到30兆赫之间,以避免干扰现有的xDSL服务。G.fast可能也会采用“开槽”,其将在特定的个别频率上对运营商进行禁止,以避免与本地射频服务相冲突。

低延迟SMC 2000 16x32G和SMC 2000 8x32G存储控制器的设计符合CXL 1.1和CXL 2.0规范、DDR4和DDR5 JEDEC标准,并支持PCIe®5.0规范速度。

SMC 2000 16x32G是业界容量最大的控制器,有16条通道,运行速度为32GT/s,支持DDR4-3200或DDR5-4800的两个通道,从而大大减少了每个存储通道所需的主机CPU或SoC引脚数量。

典型的CXL连接的存储模块包括512 GB或以上存储器,提供了有效的机制来增加处理内核事务可用的存储带宽。这种新的模式转变让数据中心运营商能够根据实际应用需求,部署更广泛的存储器与CPU内核的比例,从而提高存储器利用率,降低总拥有成本。

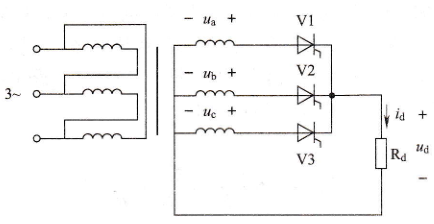

根据R3,R5的电阻,可以知道它们并联后各自分配的电流大小,与它们的电阻成反比,所以R5上的电流为1A, 对应12欧姆的电阻,产生的电压为 负12V。

电路中包括一个18V的电压源。两个电流源。要求求出电阻R5上的电压U。对于这样线性电路,可以采用电路的叠加性原理。也就是分别求出三个电源单独激励下,电阻R5上的电压。

这种TDD(时分双工)信号是与现有的FDD(频分双工)DSL信号的主要区别。

G.fast的带宽将扩展到106兆赫(有可能高达212兆赫),起始频率在2.2兆赫到30兆赫之间,以避免干扰现有的xDSL服务。G.fast可能也会采用“开槽”,其将在特定的个别频率上对运营商进行禁止,以避免与本地射频服务相冲突。

低延迟SMC 2000 16x32G和SMC 2000 8x32G存储控制器的设计符合CXL 1.1和CXL 2.0规范、DDR4和DDR5 JEDEC标准,并支持PCIe®5.0规范速度。

SMC 2000 16x32G是业界容量最大的控制器,有16条通道,运行速度为32GT/s,支持DDR4-3200或DDR5-4800的两个通道,从而大大减少了每个存储通道所需的主机CPU或SoC引脚数量。

典型的CXL连接的存储模块包括512 GB或以上存储器,提供了有效的机制来增加处理内核事务可用的存储带宽。这种新的模式转变让数据中心运营商能够根据实际应用需求,部署更广泛的存储器与CPU内核的比例,从而提高存储器利用率,降低总拥有成本。

根据R3,R5的电阻,可以知道它们并联后各自分配的电流大小,与它们的电阻成反比,所以R5上的电流为1A, 对应12欧姆的电阻,产生的电压为 负12V。

电路中包括一个18V的电压源。两个电流源。要求求出电阻R5上的电压U。对于这样线性电路,可以采用电路的叠加性原理。也就是分别求出三个电源单独激励下,电阻R5上的电压。

公网安备44030402000607

公网安备44030402000607