时钟源端门单元带载很多其负载延时很大并且不平衡

发布时间:2024/3/9 19:27:37 访问次数:91

100瓦USB-C PD电源适配器参考设计。该参考设计电路采用系统级封装(SiP)SuperGaN®电源控制芯片WT7162RHUG24A,在准谐振反激式(QRF)拓扑中可实现92.2%的效率。

第二款使用WT7162RHUG24A的QRF拓扑USB-C PD适配器控制板.65瓦的适配器控制电路。两款适配器控制板采用同一个SuperGaN SiP,与竞争方案相比,客户能够以更优的成本实现100瓦产品设计,从而实现规模效益。

这个库可以存储各种类型的设计模块,包括电路元件、接口、协议、算法等。

芯片中的时钟网络要驱动电路中所有的时序单元,所以时钟源端门单元带载很多,其负载延时很大并且不平衡,需要插入缓冲器减小负载和平衡延时。时钟网络及其上的缓冲器构成了时钟树。

在新的设计项目中,用户可以通过搜索和选择要重用的模块,将其插入到设计中。

系统会自动将模块的接口与新设计的接口进行匹配,以确保正确连接。

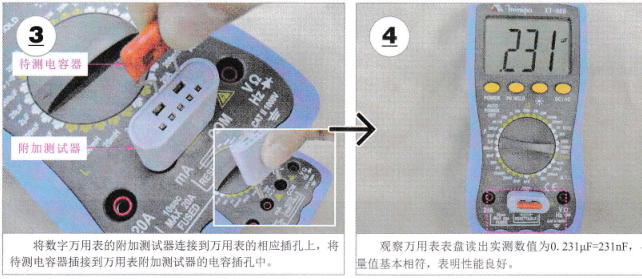

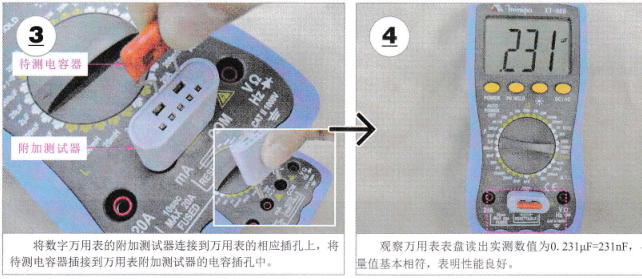

将数字万用表串联接入电路中,使电流从红表笔流入,黑表笔流出,保持稳定。

数字电桥使用方法是一种测量仪器,简单地说就是用于测量电阻、电容、电感等的仪器。

数字电桥的测量对象为阻抗元件的参数,包括交流电阻R、电感L及其品质因数o,电容C及其损耗因数D。因此,又常称数字电桥为数字式LCR测量仪。

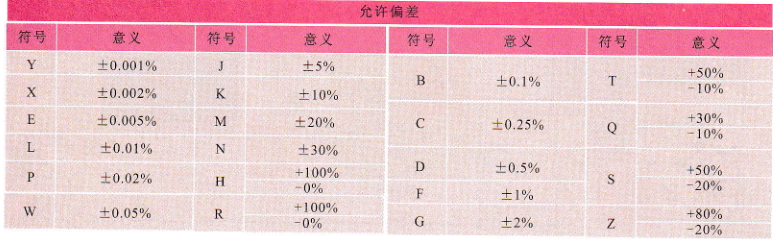

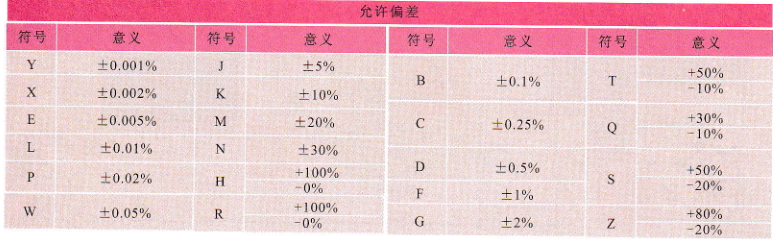

不小于luF的非电解电容,采用100Hz频率,并联(PAR)方式测量;不小于luF的电解电容,采用IOO Hz频率,串联(SER)方式测量。测量时除了观察电容器容量是否符合标称容量外,还要看D值大小。

100瓦USB-C PD电源适配器参考设计。该参考设计电路采用系统级封装(SiP)SuperGaN®电源控制芯片WT7162RHUG24A,在准谐振反激式(QRF)拓扑中可实现92.2%的效率。

第二款使用WT7162RHUG24A的QRF拓扑USB-C PD适配器控制板.65瓦的适配器控制电路。两款适配器控制板采用同一个SuperGaN SiP,与竞争方案相比,客户能够以更优的成本实现100瓦产品设计,从而实现规模效益。

这个库可以存储各种类型的设计模块,包括电路元件、接口、协议、算法等。

芯片中的时钟网络要驱动电路中所有的时序单元,所以时钟源端门单元带载很多,其负载延时很大并且不平衡,需要插入缓冲器减小负载和平衡延时。时钟网络及其上的缓冲器构成了时钟树。

在新的设计项目中,用户可以通过搜索和选择要重用的模块,将其插入到设计中。

系统会自动将模块的接口与新设计的接口进行匹配,以确保正确连接。

将数字万用表串联接入电路中,使电流从红表笔流入,黑表笔流出,保持稳定。

数字电桥使用方法是一种测量仪器,简单地说就是用于测量电阻、电容、电感等的仪器。

数字电桥的测量对象为阻抗元件的参数,包括交流电阻R、电感L及其品质因数o,电容C及其损耗因数D。因此,又常称数字电桥为数字式LCR测量仪。

不小于luF的非电解电容,采用100Hz频率,并联(PAR)方式测量;不小于luF的电解电容,采用IOO Hz频率,串联(SER)方式测量。测量时除了观察电容器容量是否符合标称容量外,还要看D值大小。

公网安备44030402000607

公网安备44030402000607