输出脚存在杂波的输出杂波将会受到MCU串口的接收和处理

发布时间:2023/12/30 21:50:43 访问次数:93

接收并保存无线接收解码模块传送的抢答成功的终端的编码并封锁接收模块,直至控制端复位;同时蜂鸣器奏响并在LED显示抢答成功的终端编号;并完成CPLD与串行接口芯片的数据交换.

该控制程序主要包括4个功能子模块:分频模块、抢答终端编码接收模块、串行发送模块、串行接收模块。在Max-f-Plus II 10. 0中设计输人各个模块的VHDL的程序后,生成库器件并合成系统原理。

模块输出数据为10位,在发送完10位后,就停止发送,并使发送端电平处于逻辑1,然后等候下次的发送。

模块将抢答终端编码接收模块输出的抢答终端的编码按照串行异步通讯规则发送给人机接口电路。

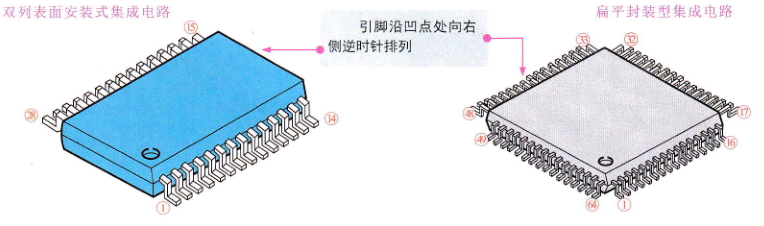

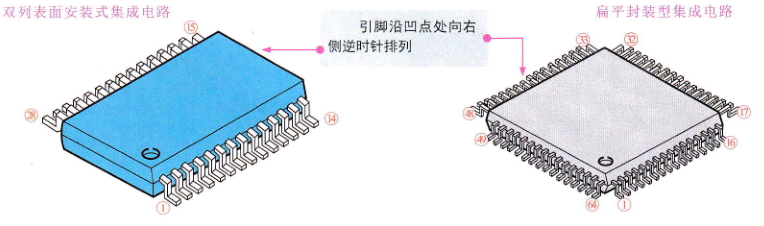

而且具有68个用户可编程的I/O接口,为系统定义输人、输出和双向口提供了极大的方便;

新的CPLD芯片技术除了大大减少集成芯片的数目,便于对系统进行扩展,还可以缩短开发周期。降低开发成本,同时提高了技术保密性。

与FPGA技术相比,CPLD有掉电不易失的优点,使用更加方便。

基于CPLD和无线编解码发射接收技术的无线抢答器系统的原理框,由8路无线抢答终端、主控制器以及上位微机系统组成。

无线发射接受模块采用通用系列产品9912,在主控制器端的无线接收模块采用的是9921,这样不仅可以加快制作过程,而且还可以增加电路的稳定与可靠性。

由于NRF401灵敏度极高,因此,若无数据的传输时,其数据的输出脚将会存在杂波的输出,此类杂波将会受到MCU串口的接收和处理。

接收并保存无线接收解码模块传送的抢答成功的终端的编码并封锁接收模块,直至控制端复位;同时蜂鸣器奏响并在LED显示抢答成功的终端编号;并完成CPLD与串行接口芯片的数据交换.

该控制程序主要包括4个功能子模块:分频模块、抢答终端编码接收模块、串行发送模块、串行接收模块。在Max-f-Plus II 10. 0中设计输人各个模块的VHDL的程序后,生成库器件并合成系统原理。

模块输出数据为10位,在发送完10位后,就停止发送,并使发送端电平处于逻辑1,然后等候下次的发送。

模块将抢答终端编码接收模块输出的抢答终端的编码按照串行异步通讯规则发送给人机接口电路。

而且具有68个用户可编程的I/O接口,为系统定义输人、输出和双向口提供了极大的方便;

新的CPLD芯片技术除了大大减少集成芯片的数目,便于对系统进行扩展,还可以缩短开发周期。降低开发成本,同时提高了技术保密性。

与FPGA技术相比,CPLD有掉电不易失的优点,使用更加方便。

基于CPLD和无线编解码发射接收技术的无线抢答器系统的原理框,由8路无线抢答终端、主控制器以及上位微机系统组成。

无线发射接受模块采用通用系列产品9912,在主控制器端的无线接收模块采用的是9921,这样不仅可以加快制作过程,而且还可以增加电路的稳定与可靠性。

由于NRF401灵敏度极高,因此,若无数据的传输时,其数据的输出脚将会存在杂波的输出,此类杂波将会受到MCU串口的接收和处理。

公网安备44030402000607

公网安备44030402000607