嵌入式CPU,FPGA管理程序或VHDL中应用程序流配置控制器

发布时间:2022/11/21 8:26:27 访问次数:133

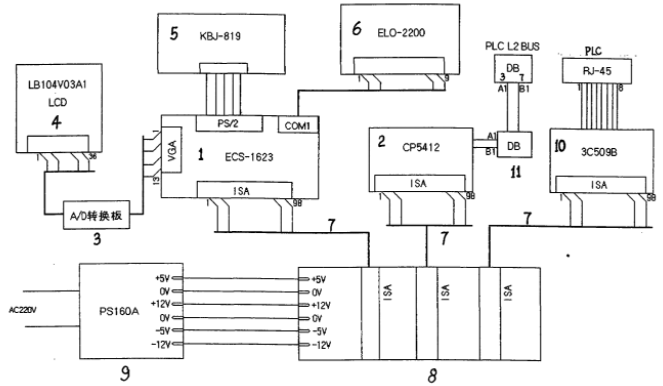

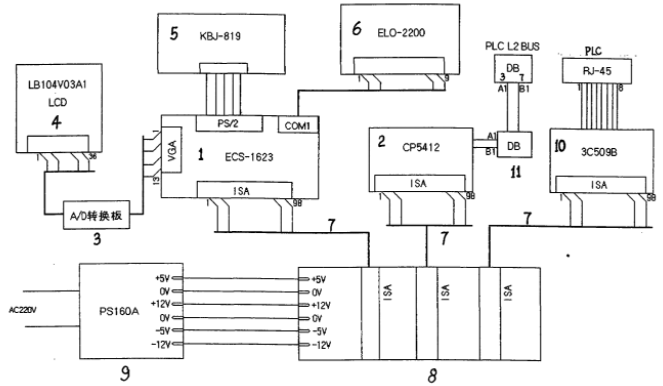

流缓冲控制器IP核为FPGA而优化,并实现了一个多功能的流到内存映射DMA桥,最多有16个独立的流。IP核允许外部内存设备中的数据缓冲,以提供高达4兆字节内存大小的虚拟FIFO能力。

它为每个写和读数据流提供了一个AMBA AXI4-Stream接口。一个公共内存映射主接口(AXI4或Avalon)可用于访问外部内存设备。

IP核高度可配置,如每个流的操作模式、缓冲区大小和缓冲区地址。配置是通过内存映射的从接口完成的,可以通过嵌入式CPU、FPGA管理程序或VHDL中的特定的应用程序流配置控制器完成。

测试、执行和金牌签核技术的独特融合使Achronix能够在系统性规模层面更大限度地减少设计余量,实现更好的整体设计收敛,并帮助Achronix加速实现首次硅成功。

ASIC要考虑SCAN测试和BIST的问题,所以设计的时候还需要为SRAM做BIST插入,需要为SCAN预留接口,虽然大部分都是工具干的,但是经常RTL作者也要手动做一些顶层工作,比如SCAN时钟的来源等逻辑。

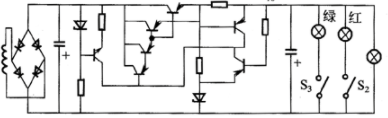

模块化的通用驱动控制器IP核包括控制频率超过200kHz的8个轴(即电机)所需的一切:从A/D转换器接口到位置、速度和电流控制器,通过编码器或解析器的位置检测,功率级的控制逻辑。支持直流,无刷直流和2或3相步进电机。

在外形银子受面积和功率限制的情况下,Fusion设计平台可帮助Achronix实现具有市场塑造力的高带宽计算所需的性能。

定制设计平台有助于减少在7纳米Speedster7t FPGA中设计、布局和模拟高性能定制电路所需的时间和精力,具有特定节点的特性,可提高开发者的工作效率。

来源:eefocus.如涉版权请联系删除。图片供参考

流缓冲控制器IP核为FPGA而优化,并实现了一个多功能的流到内存映射DMA桥,最多有16个独立的流。IP核允许外部内存设备中的数据缓冲,以提供高达4兆字节内存大小的虚拟FIFO能力。

它为每个写和读数据流提供了一个AMBA AXI4-Stream接口。一个公共内存映射主接口(AXI4或Avalon)可用于访问外部内存设备。

IP核高度可配置,如每个流的操作模式、缓冲区大小和缓冲区地址。配置是通过内存映射的从接口完成的,可以通过嵌入式CPU、FPGA管理程序或VHDL中的特定的应用程序流配置控制器完成。

测试、执行和金牌签核技术的独特融合使Achronix能够在系统性规模层面更大限度地减少设计余量,实现更好的整体设计收敛,并帮助Achronix加速实现首次硅成功。

ASIC要考虑SCAN测试和BIST的问题,所以设计的时候还需要为SRAM做BIST插入,需要为SCAN预留接口,虽然大部分都是工具干的,但是经常RTL作者也要手动做一些顶层工作,比如SCAN时钟的来源等逻辑。

模块化的通用驱动控制器IP核包括控制频率超过200kHz的8个轴(即电机)所需的一切:从A/D转换器接口到位置、速度和电流控制器,通过编码器或解析器的位置检测,功率级的控制逻辑。支持直流,无刷直流和2或3相步进电机。

在外形银子受面积和功率限制的情况下,Fusion设计平台可帮助Achronix实现具有市场塑造力的高带宽计算所需的性能。

定制设计平台有助于减少在7纳米Speedster7t FPGA中设计、布局和模拟高性能定制电路所需的时间和精力,具有特定节点的特性,可提高开发者的工作效率。

来源:eefocus.如涉版权请联系删除。图片供参考

公网安备44030402000607

公网安备44030402000607