片外驱动器阻抗调整和单芯片终端最大21dBm调整9dBm那样低

发布时间:2022/10/7 14:40:30 访问次数:87

第一个由Intel DDR2确认的512Mb DDR2 SDRAM器件EDE51xxABSE。该器件的数据传输速率高达533Mbps,工作电压1.8V,能满足下一代PC,工作站和服务器对高速低功耗的要求。它的功耗比DDR1器件要低30%。

Elpida的大容量宽带宽512Mb DDR2 SDRAM器件是采用0.11um工艺制造的。

它的结构分别为128Mx4位;64MX8为和132MX16位,采用FBGA封装。基于DDR2的器件的CAS等待3,4,突发长度4和8。器件的先进DDR2结构包括有片外驱动器阻抗调整和单芯片终端(ODT),提供更好的系统时序和提高信号质量。

EDE51xxABSE和JEDEC标准兼容,用作DDR2 DIMM基本器件。

一种大容量低成本经久耐用的称为存储元件(SE)的硬盘驱动器(HDD),尺寸只有42.8x36.4x5mm。据称,它在各种存储解决方案中有最低的成本/容量比。

为了防止工作时的机械损害,SE的传感器指令在震动的情况下主设备限制存取。该器件能经受从1米高的地方跌落到硬表面而不损坏。

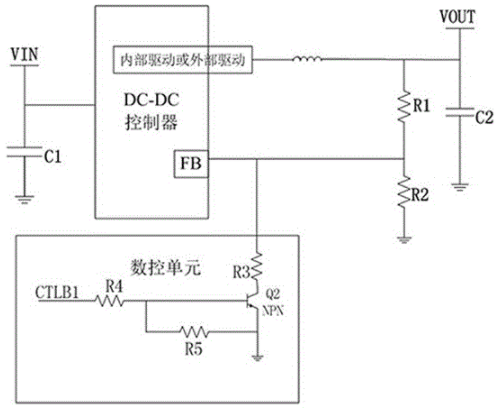

E-pHENT缓冲放大器还有"智能偏压"功能,通过改变外接电阻就能把输出功率从最大的21dBm调整到9dBm那样低。

这使它很适合用作LO缓冲放大器,驱动需要最低7dBm LO驱动的低成本7级混频器。

该器件采用0.25微米CMOS工艺,单电源2.5V工作,I/O电压和2.5V/3.3V兼容,很容易和低压数字系统接口。

转换器采用管线结构,以得到高线性。在40MSPS时,SNR为59.8dB,SINAD为57.5dB。

来源:eccn.如涉版权请联系删除。图片供参考

第一个由Intel DDR2确认的512Mb DDR2 SDRAM器件EDE51xxABSE。该器件的数据传输速率高达533Mbps,工作电压1.8V,能满足下一代PC,工作站和服务器对高速低功耗的要求。它的功耗比DDR1器件要低30%。

Elpida的大容量宽带宽512Mb DDR2 SDRAM器件是采用0.11um工艺制造的。

它的结构分别为128Mx4位;64MX8为和132MX16位,采用FBGA封装。基于DDR2的器件的CAS等待3,4,突发长度4和8。器件的先进DDR2结构包括有片外驱动器阻抗调整和单芯片终端(ODT),提供更好的系统时序和提高信号质量。

EDE51xxABSE和JEDEC标准兼容,用作DDR2 DIMM基本器件。

一种大容量低成本经久耐用的称为存储元件(SE)的硬盘驱动器(HDD),尺寸只有42.8x36.4x5mm。据称,它在各种存储解决方案中有最低的成本/容量比。

为了防止工作时的机械损害,SE的传感器指令在震动的情况下主设备限制存取。该器件能经受从1米高的地方跌落到硬表面而不损坏。

E-pHENT缓冲放大器还有"智能偏压"功能,通过改变外接电阻就能把输出功率从最大的21dBm调整到9dBm那样低。

这使它很适合用作LO缓冲放大器,驱动需要最低7dBm LO驱动的低成本7级混频器。

该器件采用0.25微米CMOS工艺,单电源2.5V工作,I/O电压和2.5V/3.3V兼容,很容易和低压数字系统接口。

转换器采用管线结构,以得到高线性。在40MSPS时,SNR为59.8dB,SINAD为57.5dB。

来源:eccn.如涉版权请联系删除。图片供参考

公网安备44030402000607

公网安备44030402000607