����������ź���оƬ�ߴ�С��ͬ�ྺ�����������1/3

����ʱ��:2022/5/13 18:24:29 ���ʴ���:169

5x5����QFN��װ�ĵ͵�ѹ����ź�(LVDS)��������(SerDes)��

оƬ�ijߴ�С��ͬ�ྺ�����������1/3���ܹ�������С����Ӧ�õİ弶�ռ䣬������վ������ͨ�ű��塢��ҵ����Ƶϵͳ�Լ�������Ϣ��������Ƶϵͳ��Ӧ�á�

SN65LV1023A��������SN65LV1224B�������10λSerDesоƬ�飬��ͨ��LVDS��ֱ������൱�ڲ����ֵ�ʱ������(10MHz-66MHz)�շ��������ݡ�

��һ���ʷ�Χ��Ӧ����������ΧΪ100Mbps��660Mbps��

¶������Ƭ��о�߷���Ҫ��

¶������Ƭ��о�߳���

��ԵͲѹ�Ӻ���

��ԵͲ����˺�Ѻۼ�

���߾�Ե�����ԵͲλ�ú���

���߾�Ե���˽���Ƭ��ѹ��Ͳ

��ԵͲû��ѹס���߾�Ե

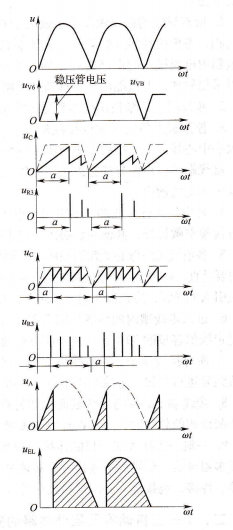

����ʱ�䦲-��(CTSD)ģ��ת����(ADC)��������·�ļܹ����ԣ����ּܹ��ܹ���ADCģ������˵��ź�����ơ�

ADC�ܹ��еĴ�ͳ��������ת����������ȱ�㡣

�첽��������ת��(ASRC)���������κ�ADC�ܹ���ԣ��Ի���κ����������������ʣ������ⲿ�������������ֽӿ���ơ�ASRC��CTSD ADC�����ν��ȫ�����������ܼ�ADCģ������˵��ź�����ƣ�Ҳ�ܼ���������˵��ź�����ơ�

5x5����QFN��װ�ĵ͵�ѹ����ź�(LVDS)��������(SerDes)��

оƬ�ijߴ�С��ͬ�ྺ�����������1/3���ܹ�������С����Ӧ�õİ弶�ռ䣬������վ������ͨ�ű��塢��ҵ����Ƶϵͳ�Լ�������Ϣ��������Ƶϵͳ��Ӧ�á�

SN65LV1023A��������SN65LV1224B�������10λSerDesоƬ�飬��ͨ��LVDS��ֱ������൱�ڲ����ֵ�ʱ������(10MHz-66MHz)�շ��������ݡ�

��һ���ʷ�Χ��Ӧ����������ΧΪ100Mbps��660Mbps��

¶������Ƭ��о�߷���Ҫ��

¶������Ƭ��о�߳���

��ԵͲѹ�Ӻ���

��ԵͲ����˺�Ѻۼ�

���߾�Ե�����ԵͲλ�ú���

���߾�Ե���˽���Ƭ��ѹ��Ͳ

��ԵͲû��ѹס���߾�Ե

����ʱ�䦲-��(CTSD)ģ��ת����(ADC)��������·�ļܹ����ԣ����ּܹ��ܹ���ADCģ������˵��ź�����ơ�

ADC�ܹ��еĴ�ͳ��������ת����������ȱ�㡣

�첽��������ת��(ASRC)���������κ�ADC�ܹ���ԣ��Ի���κ����������������ʣ������ⲿ�������������ֽӿ���ơ�ASRC��CTSD ADC�����ν��ȫ�����������ܼ�ADCģ������˵��ź�����ƣ�Ҳ�ܼ���������˵��ź�����ơ�

�������

�������

- ��Ƭ����������������Լ������Զ�����װ�豸

- �����Ƶ��Χ�Ͷ�������ӿ���������ҪI/O��

- 1.0mm��ż��BGA��װС30������㾫

- FIM���ϸ��������źŵ�ǰ�ĸߵ�ƽ��·

- 3G��Ƶ�ļ��ȴ��ļ���IrDA�����������ӵ�

- �Ž�оƬ��Ƕ��ʽUSB2.0 Link������

- �����ƶ����ƻ��ڵ��ݶ��������������ԭ��

- 32KW��ǶFinFET��ǽ��Ⱥ�Դ©������

- ������ʩ����״̬�����ó����������״̬����

- ���ʾ�բ�ܴ�����·�в�������������������

�Ƽ���������

�Ƽ���������

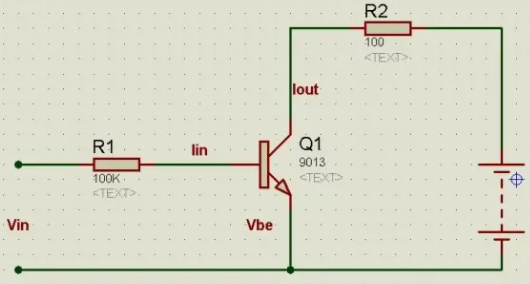

- ����ѹ���ṩ

- ��ʼ��ʱ����ʹ��LM385��Ϊ����HIN202EC... [��ϸ]

��������44030402000607

��������44030402000607