PCB层数从而降低PCB的生产成本先进高速接口的FPGA

发布时间:2022/1/28 18:17:26 访问次数:128

多FPGA原型板并不总是能满足设计师的要求,使用这种FPGA I/O综合技术,设计者可创造出一个新的原型系统,同时比使用标准的引脚优化手工方式快得多的时间找出多种互联与组件的设计方法。FPGA System Planner缩减了将FPGA整合到PCB的时间,通过FPGA资源的最佳化使用,增强了FPGA的性能,并通过减少密集布局、复杂和大量引脚数的 FPGA所需的PCB层数从而降低了PCB的生产成本。

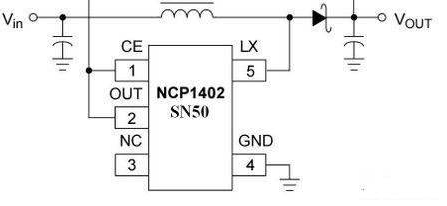

决定外部电阻使用哪个值是一个迭代且彼此相关的过程,可能的增益值相互作用,对选择使用的电阻产生影响.为了便于参考,常见的增益值组成值,但是,还可能存在许多其他的增益组合(G)。

CMP设备是半导体制造的关键工艺装备之一。CMP是集成电路制造大生产上产出效率最高、技术最成熟、应用最广泛的纳米级全局平坦化表面制造设备,并且在较长时间内不存在技术迭代周期。

而且随着芯片制造技术发展,CMP工艺在集成电路生产流程中的应用次数逐步增加,将进一步增加 CMP设备的需求。

根据SEMI,2018年全球CMP设备的市场规模18.42亿美元,约占晶圆制造设备4%的市场份额,其中中国大陆CMP设备市场规模4.59亿美元。

这些FPGAs还具有更高级的存储器接口、更低的功耗,从而解决客户对开发更加“绿色”的产品需要。使用这种更大容量、更多功能和先进高速接口的FPGA,在PCB系统中、以及在PCB上使用FPGA进行ASIC.模拟的数目正在增加。

Taray公司的技术将成为Cadence公司产品一个强有力的组合。

领先业界的NX27V向量处理器于去年底获得EE Times颁发的EDA和IP产品奖,并已被采用于近10个客户多核架构的云端加速器之中。

(素材来源:转载自网络,如涉版权请联系删除,特别感谢)

多FPGA原型板并不总是能满足设计师的要求,使用这种FPGA I/O综合技术,设计者可创造出一个新的原型系统,同时比使用标准的引脚优化手工方式快得多的时间找出多种互联与组件的设计方法。FPGA System Planner缩减了将FPGA整合到PCB的时间,通过FPGA资源的最佳化使用,增强了FPGA的性能,并通过减少密集布局、复杂和大量引脚数的 FPGA所需的PCB层数从而降低了PCB的生产成本。

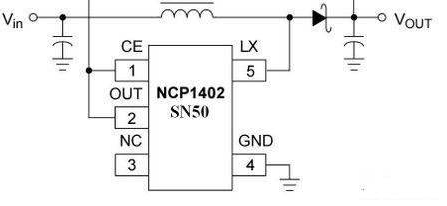

决定外部电阻使用哪个值是一个迭代且彼此相关的过程,可能的增益值相互作用,对选择使用的电阻产生影响.为了便于参考,常见的增益值组成值,但是,还可能存在许多其他的增益组合(G)。

CMP设备是半导体制造的关键工艺装备之一。CMP是集成电路制造大生产上产出效率最高、技术最成熟、应用最广泛的纳米级全局平坦化表面制造设备,并且在较长时间内不存在技术迭代周期。

而且随着芯片制造技术发展,CMP工艺在集成电路生产流程中的应用次数逐步增加,将进一步增加 CMP设备的需求。

根据SEMI,2018年全球CMP设备的市场规模18.42亿美元,约占晶圆制造设备4%的市场份额,其中中国大陆CMP设备市场规模4.59亿美元。

这些FPGAs还具有更高级的存储器接口、更低的功耗,从而解决客户对开发更加“绿色”的产品需要。使用这种更大容量、更多功能和先进高速接口的FPGA,在PCB系统中、以及在PCB上使用FPGA进行ASIC.模拟的数目正在增加。

Taray公司的技术将成为Cadence公司产品一个强有力的组合。

领先业界的NX27V向量处理器于去年底获得EE Times颁发的EDA和IP产品奖,并已被采用于近10个客户多核架构的云端加速器之中。

(素材来源:转载自网络,如涉版权请联系删除,特别感谢)

公网安备44030402000607

公网安备44030402000607