DC2247A基本D触发器

发布时间:2019/10/16 21:21:13 访问次数:1138

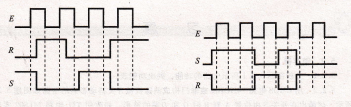

DC2247A锁存器和触发器的Veri|og建模实例本节给出一些锁存器和触发器的行为级描述实例。例5.5.1是D锁存器的描述,它有两个输入(D和E)(1个输出(Q)。对于锁存器来说,当输入控制信号处于有效电平时(即E=1时),其输出Q跟随输入信号D的变化;当控制信号无效时,输出Q保持不变。所以在anways语句中@符号之后的“事件控制表达式”使用了电平敏感事件,说明如果输人信号E或者D发生变化,

就会执行一次后面的if语句,但只有E为逻辑1时,输入D的变化才能传送到输出Q;否则,输出Q将保持不变。注意,由于输出Q是在过程语句中被赋值,所以必须将它声明为reg类型的变量。

例5,5.1

//Description of D 1atch(See Fig. 5.2.10a or Fig. 5.2.11a)

nlodule D~latch(Q,D,E);

output Q;

input D, E;

reg Q;

always@(E or D)

iF(E)Q (= D;

endInodule

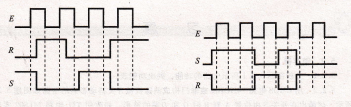

例5.5.2中描述了三种上升沿触发的D触发器。第一个模块描述的是功能如图5.3.2或图5.3,5那样的基本D触发器,其输出信号为Q,输人信号为D和CP。由于是在过程语句中被赋值,输出信号Q必须声明为reg型变量。在a1ways语句@符号之后的“事件控制表达式”中使用了边沿触发事件,即posedge CP,使其后的语句Q(=D仅在CP上升沿期间将D的值赋给Q,而在其他任何时间,无论D信号如何变化,都不能改变Q的状态。

例5.5,2中第二个模块描述了如图5.3.3或图5.3,6所示具有异步直接置1、置0功能的D触发器。在always语句的“事件控制表达式”中,比前一模块增加了两个异步触发事件negedge sd和negedge Rd。在这种表达式中,可以有一个或多个异步事件,但必须有一个事件是时钟事件,它们之间用关键词or进行连接。这个模块中的触发事件表示,在输入信号CP的上升沿到来时,或sd或Rd跳变为低电平时,后面的if-e1se语句就会被执行一次。negedge sd和negedge Rd是两个异步事件,它与if(~sd‖~Rd)语句相匹配。如果条件具备,接下来,如果sd为逻辑0(if(~sd)),则将输出Q置1,QN置0;否则(else)将输出Q置0,QN置1;如果sd和Rd均不为0,只能是时钟CP上升沿到来,则将输人D传送到输出Q, ~D传送到QN。从语句执行的顺序可以看出,如果直接置1或置0事件和时钟事仵同时发生,则置1或置0事件有更高的优先级别,这与图5.3.3或图5,3.6中电路的功能是一致的。

系Non~Blocking Assignment Statcmcnt的译称。

DC2247A锁存器和触发器的Veri|og建模实例本节给出一些锁存器和触发器的行为级描述实例。例5.5.1是D锁存器的描述,它有两个输入(D和E)(1个输出(Q)。对于锁存器来说,当输入控制信号处于有效电平时(即E=1时),其输出Q跟随输入信号D的变化;当控制信号无效时,输出Q保持不变。所以在anways语句中@符号之后的“事件控制表达式”使用了电平敏感事件,说明如果输人信号E或者D发生变化,

就会执行一次后面的if语句,但只有E为逻辑1时,输入D的变化才能传送到输出Q;否则,输出Q将保持不变。注意,由于输出Q是在过程语句中被赋值,所以必须将它声明为reg类型的变量。

例5,5.1

//Description of D 1atch(See Fig. 5.2.10a or Fig. 5.2.11a)

nlodule D~latch(Q,D,E);

output Q;

input D, E;

reg Q;

always@(E or D)

iF(E)Q (= D;

endInodule

例5.5.2中描述了三种上升沿触发的D触发器。第一个模块描述的是功能如图5.3.2或图5.3,5那样的基本D触发器,其输出信号为Q,输人信号为D和CP。由于是在过程语句中被赋值,输出信号Q必须声明为reg型变量。在a1ways语句@符号之后的“事件控制表达式”中使用了边沿触发事件,即posedge CP,使其后的语句Q(=D仅在CP上升沿期间将D的值赋给Q,而在其他任何时间,无论D信号如何变化,都不能改变Q的状态。

例5.5,2中第二个模块描述了如图5.3.3或图5.3,6所示具有异步直接置1、置0功能的D触发器。在always语句的“事件控制表达式”中,比前一模块增加了两个异步触发事件negedge sd和negedge Rd。在这种表达式中,可以有一个或多个异步事件,但必须有一个事件是时钟事件,它们之间用关键词or进行连接。这个模块中的触发事件表示,在输入信号CP的上升沿到来时,或sd或Rd跳变为低电平时,后面的if-e1se语句就会被执行一次。negedge sd和negedge Rd是两个异步事件,它与if(~sd‖~Rd)语句相匹配。如果条件具备,接下来,如果sd为逻辑0(if(~sd)),则将输出Q置1,QN置0;否则(else)将输出Q置0,QN置1;如果sd和Rd均不为0,只能是时钟CP上升沿到来,则将输人D传送到输出Q, ~D传送到QN。从语句执行的顺序可以看出,如果直接置1或置0事件和时钟事仵同时发生,则置1或置0事件有更高的优先级别,这与图5.3.3或图5,3.6中电路的功能是一致的。

系Non~Blocking Assignment Statcmcnt的译称。

上一篇:DC2857A 串行语句块

热门点击

热门点击

- BS250优先编码器74HC147

- 环网柜DTU与开闭所DTU的比较

- 光纤通信的优点

- 行列码校验又称为方阵码校验或者水平垂直奇偶校

- 重合器(Recbser)是用于配电网自动化的

- 74435586800 四变量卡诺图

- 通信规约的概念

- 站控终端的概念及功能

- 自愈式光纤系统

- NUs系统选线下位机软件设计

推荐技术资料

推荐技术资料

- 业余条件下PCM2702

- PGM2702采用SSOP28封装,引脚小而密,EP3... [详细]

公网安备44030402000607

公网安备44030402000607