S202S11 D触发器的特性方程

发布时间:2019/10/16 12:27:43 访问次数:2756

QN+1=D (5・3・1)

称为D触发器的特性方程。它反映了触发器在时钟信号作用后的状态与此前输入信号D的关系。

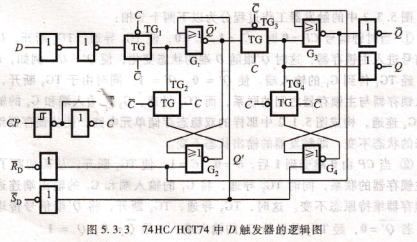

典型集成电路,图5,3.3是以图5.3,2中电路为基础构成的集成CMOS D触发器的内部逻辑电路。由于实际应用中有时需要对触发器进行异步(即与图中CP信号无关)复位、置位,所以电路中引入了直接置0端RD和直接置1端sD,这两个信号经非门缓冲后,送入主锁存器和从锁存器。从图中看出,当TG1、TG4断开而TG,、TG3导通,即CP=1时,或非门G1和G2构成图5.2,1(a)所示的基本sR锁存器,可以把直接置0或置1信号锁存到Q′和Q′端,进而传送到O和口端。当TG3断开,TG4导通,即CP=0时,或非门G3和G4构成基本sR锁存器,同样可把直接置0或置1信号锁存到Q和口端。由图可见,电路中所有输出端都设置了输出缓冲电路,所有输人端也都设置了输人缓冲电路,这是新型CMOs集成电路的特点之一,它提高了电路工作的稳定性。为了避免CP脉冲上升沿或下降沿在跨越阈值电平时的噪声引发触发器的误触发,电路在CP输入端特别设置了施密特反相器以提高抗干扰能力(施密特电路的抗干扰原理见8.3节)。

QN+1=D (5・3・1)

称为D触发器的特性方程。它反映了触发器在时钟信号作用后的状态与此前输入信号D的关系。

典型集成电路,图5,3.3是以图5.3,2中电路为基础构成的集成CMOS D触发器的内部逻辑电路。由于实际应用中有时需要对触发器进行异步(即与图中CP信号无关)复位、置位,所以电路中引入了直接置0端RD和直接置1端sD,这两个信号经非门缓冲后,送入主锁存器和从锁存器。从图中看出,当TG1、TG4断开而TG,、TG3导通,即CP=1时,或非门G1和G2构成图5.2,1(a)所示的基本sR锁存器,可以把直接置0或置1信号锁存到Q′和Q′端,进而传送到O和口端。当TG3断开,TG4导通,即CP=0时,或非门G3和G4构成基本sR锁存器,同样可把直接置0或置1信号锁存到Q和口端。由图可见,电路中所有输出端都设置了输出缓冲电路,所有输人端也都设置了输人缓冲电路,这是新型CMOs集成电路的特点之一,它提高了电路工作的稳定性。为了避免CP脉冲上升沿或下降沿在跨越阈值电平时的噪声引发触发器的误触发,电路在CP输入端特别设置了施密特反相器以提高抗干扰能力(施密特电路的抗干扰原理见8.3节)。

热门点击

热门点击

- BS250优先编码器74HC147

- 施密特触发器用在去抖电路中的工作原理

- 程序存储器和数据存储器具有各自的总线

- 环网柜DTU与开闭所DTU的比较

- 光纤通信的优点

- 行列码校验又称为方阵码校验或者水平垂直奇偶校

- 重合器(Recbser)是用于配电网自动化的

- 74435586800 四变量卡诺图

- 通信规约的概念

- 站控终端的概念及功能

推荐技术资料

推荐技术资料

- 业余条件下PCM2702

- PGM2702采用SSOP28封装,引脚小而密,EP3... [详细]

公网安备44030402000607

公网安备44030402000607