448510091 模块完成的逻辑功能

发布时间:2019/10/10 13:23:52 访问次数:1053

448510091

delta=2.13;

end

integer i;//定义一个整型变量i

initial

i=delta;//i得到的值是2(只将实数2.13的整数部分赋给i)

tme型变量主要用于存储仿真的时间,它只存储无符号数。每个time型

变量存储一个至少64位的时间值。为了得到当前的仿真时间,常调用系统函

数$ume。time型变量的应用举例如下:

time current time;//定义一个时间类型的变量current~time

initial

c urrent_time=$dme;//保存当前的仿真时间到变量current~time中

delta=4e10;//给delta赋值

module模块名(端口名1,端口名2,端口名3,…);

端口类型说明(input,outouⅢnout);

参数定义(可选);

数据类型定义(wire,reg等);

说明部分

实例化低层模块和基本门级元件;

连续赋值语句(assign);

过程块结构(inidal和always)

行为描述语句;

endmoduIe

其中,“模块名”是模块唯一的标识符,圆括号中以逗号分隔列出的端口名是该模块的输人端口、输出端口;在Ⅴerilog中, “端口类型说明”为input(输入端口)、output(输出端口)、inout(双向端口)三者之一,凡是在模块名后面圆括号中出现的端口名,都必须明确地说明其端口类型。“参数定义”是将常量用符号常量代替,以增加程序的可读性和可修改性,它是一个可选择的语句。“数据类型定义”部分用来指定模块内所用的数据对象为寄存器类型还是连线类型。

接着要对该模块完成的逻辑功能进行描述,通常可以使用三种不同风格描

述电路的功能:一是使用实例化低层模块的方法,.即调用其他已定义好的低层

模块对整个电路的功能进行描述,或者直接调用Ⅴerilog内部基本门级元件描

述电路的结构,通常将这种方法称为结构描述方式;二是使用连续赋值语句对

电路的逻辑功能进行描述,通常称之为数据流描述方式,对组合逻辑电路建模

使用该方式特别方便;三是使用过程块语句结构(包括intial语句结构和a⒈

ways语句结构两种)和比较抽象的高级程序语句对电路的逻辑功能进行描述,

通常称之为行为描述方式。行为描述侧重于描述模块的行为功能,不涉及实现

该模块逻辑功能的详细硬件电路结构。行为描述方式是学习的重点。设计人员可以选用这三种方式中的任意一种或混合使用几种描述电路的逻辑功能,并且在程序中排列的先后顺序是任意的。这些描述方式将在4,6节、5,5节和6.6

节详细介绍。除此之外,还有一种开关级描述方式,专门对MOs管构成的逻辑电路进行建模,将在3.7节中介绍。

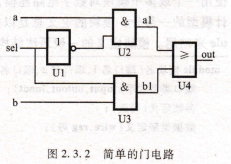

图2.3.2所示为一简单数字逻辑电路,下面介绍该电路的Verilog模型。

448510091

delta=2.13;

end

integer i;//定义一个整型变量i

initial

i=delta;//i得到的值是2(只将实数2.13的整数部分赋给i)

tme型变量主要用于存储仿真的时间,它只存储无符号数。每个time型

变量存储一个至少64位的时间值。为了得到当前的仿真时间,常调用系统函

数$ume。time型变量的应用举例如下:

time current time;//定义一个时间类型的变量current~time

initial

c urrent_time=$dme;//保存当前的仿真时间到变量current~time中

delta=4e10;//给delta赋值

module模块名(端口名1,端口名2,端口名3,…);

端口类型说明(input,outouⅢnout);

参数定义(可选);

数据类型定义(wire,reg等);

说明部分

实例化低层模块和基本门级元件;

连续赋值语句(assign);

过程块结构(inidal和always)

行为描述语句;

endmoduIe

其中,“模块名”是模块唯一的标识符,圆括号中以逗号分隔列出的端口名是该模块的输人端口、输出端口;在Ⅴerilog中, “端口类型说明”为input(输入端口)、output(输出端口)、inout(双向端口)三者之一,凡是在模块名后面圆括号中出现的端口名,都必须明确地说明其端口类型。“参数定义”是将常量用符号常量代替,以增加程序的可读性和可修改性,它是一个可选择的语句。“数据类型定义”部分用来指定模块内所用的数据对象为寄存器类型还是连线类型。

接着要对该模块完成的逻辑功能进行描述,通常可以使用三种不同风格描

述电路的功能:一是使用实例化低层模块的方法,.即调用其他已定义好的低层

模块对整个电路的功能进行描述,或者直接调用Ⅴerilog内部基本门级元件描

述电路的结构,通常将这种方法称为结构描述方式;二是使用连续赋值语句对

电路的逻辑功能进行描述,通常称之为数据流描述方式,对组合逻辑电路建模

使用该方式特别方便;三是使用过程块语句结构(包括intial语句结构和a⒈

ways语句结构两种)和比较抽象的高级程序语句对电路的逻辑功能进行描述,

通常称之为行为描述方式。行为描述侧重于描述模块的行为功能,不涉及实现

该模块逻辑功能的详细硬件电路结构。行为描述方式是学习的重点。设计人员可以选用这三种方式中的任意一种或混合使用几种描述电路的逻辑功能,并且在程序中排列的先后顺序是任意的。这些描述方式将在4,6节、5,5节和6.6

节详细介绍。除此之外,还有一种开关级描述方式,专门对MOs管构成的逻辑电路进行建模,将在3.7节中介绍。

图2.3.2所示为一简单数字逻辑电路,下面介绍该电路的Verilog模型。

公网安备44030402000607

公网安备44030402000607